# InAmp with external *R<sub>G</sub>* and offset compensation based on Miller type OpAmp

Aaron Speicher August, 2023

Supervisor Prof. Dr.-Ing. Andreas König

#### Overview

- I. Miller OpAmp

- 1. Schematic and minimum specifications

- 2. Schematic simulation and parameter adjustments

- 3. Layout design

- 4. Post layout simulation

- II. InAmp

- 1. Layout design

- 2. Post layout simulation

#### Miller OpAmp Schematic and minimum requirements

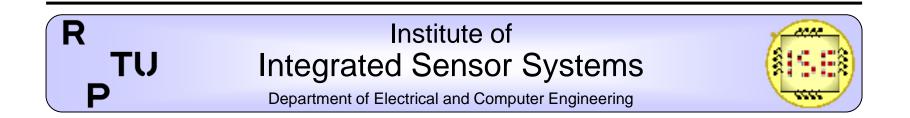

#### Schematic

- Stage 1: differential amplifier with pmos current mirror load and single-ended output

- Stage 2: common-source amplifier with a large miller capacitor

- M5 quiescent current set by separate biasing circuit

- Miller compensation capacitor improves stability at the cost of bandwidth

#### Miller OpAmp Schematic and minimum requirements

#### **Minimum requirements**

| Open Loop Gain      | 80 dB   |

|---------------------|---------|

| Gain Bandwidth      | 1 MHz   |

| Phase Margin        | 60°     |

| Common Mode Range + | 0.75 V  |

| Common Mode Range - | -0.75 V |

| Settling Time       | < 1 µs  |

| Slew Rate           | 1 V/µs  |

| Offset              | minimum |

| CMRR                | 80 dB   |

| Power Dissipation   | minimum |

| Load Capacitance    | 10 pF   |

- Minimum requirements for acceptable performance

- Miller OpAmp used to design InAmp in later stage of the project

- Higher Open Loop Gain, Slew Rate and Settling time than minimum specification further improve InAmp performance

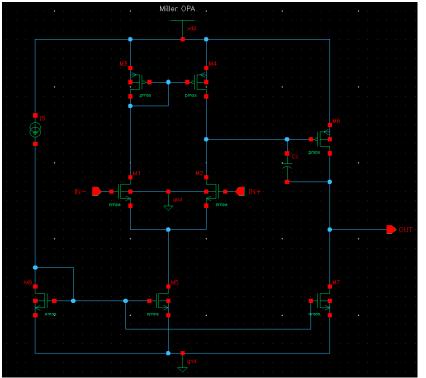

#### Miller OpAmp Simulation schematics

#### Miller OpAmp

#### Schematic simulation and parameter adjustments

Implementing the before calculated design parameters in the schematic and running all simulations resulted in the following specification:

| Open Loop Gain         | 77 dB    |

|------------------------|----------|

| Gain Bandwidth         | 976 kHz  |

| Phase Margin           | 73°      |

| Common Mode<br>Range + | 1.52 V   |

| Common Mode<br>Range - | -1.30 V  |

| Settling Time          | 0.77 μs  |

| Slew Rate              | 1 V/μs   |

| Offset                 | 80 µV    |

| CMRR                   | 86.64 dB |

- Open Loop Gain and Gain Bandwidth below minimum spec, high Offset

- Excessive Phase Margin

- Slew Rate and Common Mode Rejection Ratio match minimum spec but improvement for better InAmp performance useful

#### Miller OpAmp

#### Schematic simulation and parameter adjustments

#### **Design Approach to improve simulation results**

- Hand model transistor equations give hint on the effect of certain design parameters

- Simulator uses much more complex transistor models

➢ Impact of certain parameters might differ from expectation

#### Solution

• Combine hand model transistor equations with iterative circuit simulation and manual refinement based on experience with the circuit

#### Miller OpAmp

#### Schematic simulation and parameter adjustments

#### **Design route**

| Design change                     | Specification<br>after<br>Allen/Holberg | Cc -> 1.8pF | I5 -> 4 | I5 -> 10 | \$6, \$7 -><br>30 | S1, S2 -> 2 | \$1, \$2 -><br>3 | S7 -> 35 | S6 -> 31 | Final simulation |   |          |

|-----------------------------------|-----------------------------------------|-------------|---------|----------|-------------------|-------------|------------------|----------|----------|------------------|---|----------|

|                                   |                                         |             |         |          |                   |             |                  |          |          |                  | C | c -> 1.6 |

| Open Loop Gain in dB              | 77                                      | *           | 78      | 77       | 79                | 82          | 83               | -        | -        | 81.6             |   |          |

| Gain Bandwidth in MHz             | 0.976                                   | 1.15        | 1.65    | 2.67     | 2.80              | 3.8         | 4.6              | -        | -        | 4.6              |   | -        |

| Phasemargin in °                  | 73                                      | 71          | 69      | 66       | 72                | 66          | 62               | -        | -        | 63               |   | 5.05     |

| Common Mode Range - in V          | 1.52                                    | -           | -       | -1.3     | -                 | -           | *                | -        | -        | *                |   | 60.7     |

| Common Mode Range + in V          | -1.30                                   | -           | -       | 1.3      | -                 | -           | *                | -        | -        | 1.22             |   | -        |

| Settling Time in µs               | 0.77                                    | -           | -       | -        | -                 | -           | -                | -        | -        | -                |   | -        |

| Slew Rate in µs                   | 1                                       | 1.22        | 2.19    | 4.2      | 5.3               | 5.4         | *                | -        | -        | *                |   | 6.07     |

| Common Mode Rejection Ratio in dB | 86.64                                   | -           | -       | 82       | *                 | 91          | 100              | -        | -        | 99.83            |   | -        |

| Offset in µV                      | 80                                      | -           | -       | -        | -                 | -           | 90               | 35       | 7.21     | *                |   | -        |

|                                   |                                         |             |         |          |                   |             |                  |          |          |                  |   | -        |

| S1, S2                            | 1                                       | *           | *       | *        | *                 | 2           | 3                | *        | *        | *                |   |          |

| S3, S4                            | 1                                       | *           | *       | *        | *                 | *           | *                | *        | *        | *                |   | *        |

| S6                                | 20                                      | *           | *       | *        | 30                | *           | *                | *        | 31       | *                |   | *        |

| S7                                | 20                                      | *           | *       | *        | 30                | *           | *                | 35       | *        | *                |   | *        |

| S5                                | 2                                       | *           | *       | *        | *                 | *           | *                | *        | *        | *                |   | *        |

| I5 in μA                          | 2.21                                    | *           | 4       | 10       | *                 | *           | *                | *        | *        | *                |   | *        |

| Cc in µF                          | 2.21                                    | 1.8         | *       | *        | *                 | *           | *                | *        | *        | *                |   | 1.6      |

#### Miller OpAmp Schematic simulation and parameter adjustments

| Open Loop Gain in dB<br>Gain Bandwidth in MHz<br>Phasemargin in °<br>Common Mode Range - in V | Specification after<br>Allen/Holberg<br>77<br>0.976<br>73<br>1.52 | Design<br>Result<br>81.6<br>4.59<br>63°<br>1.22 | Cc -> 1.6pF ?<br>81.6<br>5.05<br>60.7<br>1.22 | Further improvement but<br>high chance of Phase |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------|-------------------------------------------------|

| Common Mode Range + in V                                                                      | -1.30                                                             | -1.3                                            | -1.3                                          | Margin requirement not                          |

| Settling Time in µs                                                                           | 0.77                                                              | 0.21                                            | 0.22                                          | being met after layout                          |

| Slew Rate in µs                                                                               | 1                                                                 | 5.42                                            | 6.07                                          | and extract, Cc kept at                         |

| Common Mode Rejection Ratio in dB                                                             | 86.64                                                             | 99.83                                           | 99.83                                         | 1.8pF                                           |

| Offset in µV                                                                                  | 80                                                                | 7.22                                            | 7.22                                          |                                                 |

|                                                                                               |                                                                   |                                                 |                                               |                                                 |

| S1, S2                                                                                        | 1                                                                 | 3                                               | 3                                             |                                                 |

| S3, S4                                                                                        | 1                                                                 | 1                                               | 1                                             |                                                 |

| S6                                                                                            | 20                                                                | 31                                              | 31                                            |                                                 |

| S7                                                                                            | 20                                                                | 35                                              | 35                                            |                                                 |

| S5                                                                                            | 2                                                                 | 2                                               | 2                                             |                                                 |

| I5 in μA                                                                                      | 2.21                                                              | 10                                              | 10                                            |                                                 |

| Cc in µF                                                                                      | 2.21                                                              | 1.8                                             | 1.6                                           |                                                 |

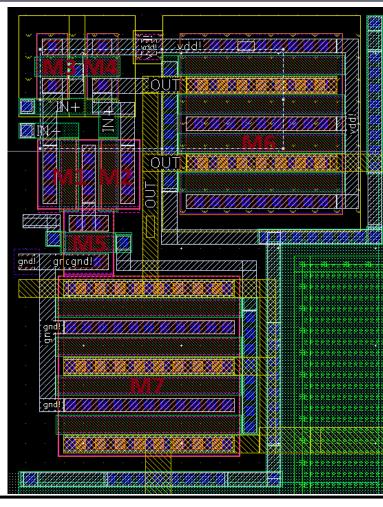

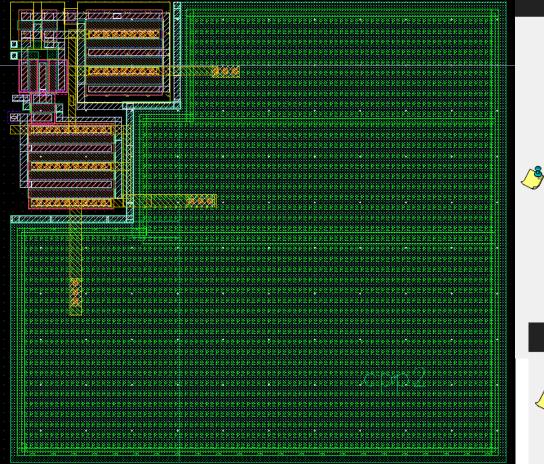

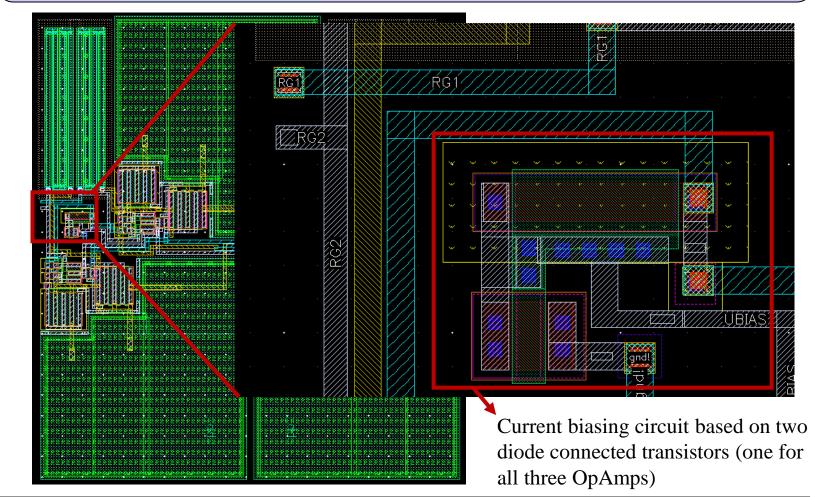

#### Miller OpAmp Layout design

- Transistors must be designed to achieve acceptable W/L ratio in the complete layout

- ➢ Folded layout for M6 and M7

- Folded layout not necessary for M1 and M2 but would result in better matching, less parasitics

- Arranging the transistors to form a close to perfect square not necessary

- Fill out space with large Miller capacitor to achieve desired chip level W/L ratio

#### Miller OpAmp Layout design

#### Layout without Cc

- Arrangement should not have too many corners

- Minimize area by using minimum design rules

R

#### Miller OpAmp Layout design

#### Layout with Cc

#### Run: "MILLER\_LVS" (auf iseserver002)

Run: "MILLER\_LVS" from /home/tl23\_speicher/AssuraLVS

Schematic and Layout Match. You currently have an open run (project).

Do you want to close current project and view the results of new run?

Summary of LVS Issues

Extraction Information:

0 cells have 0 mal-formed device problems 0 cells have 0 label short problems 0 cells have 0 label open problems

Comparison Information:

0 cells have 0 Net mismatches 0 cells have 0 Device mismatches 0 cells have 0 Pin mismatches 0 cells have 0 Parameter mismatches

ELW Information:

Total DRC violations: 0

The Quantus run "MILLER\_LVS" completed successfully The output is in :

Library: TESYS\_PROJECT\_AS Cell: MILLER View: analog\_extracted

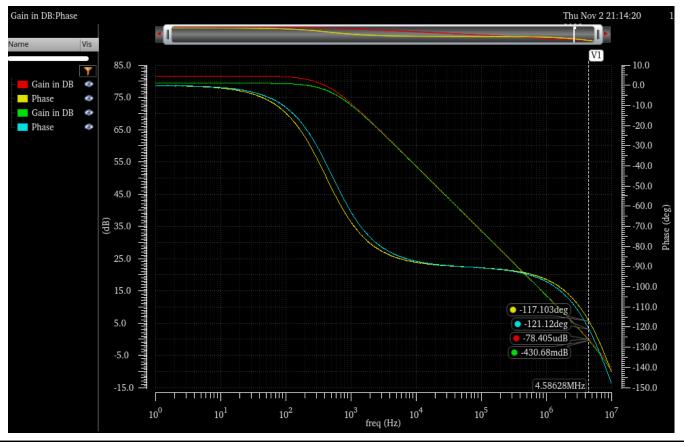

|                                   | Specification after<br>Allen/Holberg | Design<br>Result | Post Layout |

|-----------------------------------|--------------------------------------|------------------|-------------|

|                                   |                                      |                  |             |

| Open Loop Gain in dB              | 77                                   | 81.6             | 79.4        |

| Gain Bandwidth in MHz             | 0.976                                | 4.59             | 4.40        |

| Phasemargin in °                  | 73                                   | 63°              | 60          |

| Common Mode Range - in V          | 1.52                                 | 1.22             | 1.22        |

| Common Mode Range + in V          | -1.30                                | -1.3             | -1.3        |

| Settling Time in µs               | 0.77                                 | 0.21             | 0.22        |

| Slew Rate in V/µs                 | 1                                    | 5.51             | 5.46        |

| Common Mode Rejection Ratio in dB | 86.64                                | 99.83            | 99.35       |

| Offset in µV                      | 80                                   | 7.22             | 13.83       |

|                                   |                                      |                  |             |

| S1, S2                            | 1                                    | 3                | 3           |

| S3, S4                            | 1                                    | 1                | 1           |

| <b>S</b> 6                        | 20                                   | 31               | 31          |

| S7                                | 20                                   | 35               | 35          |

| <b>S</b> 5                        | 2                                    | 2                | 2           |

| I5 in µA                          | 2.21                                 | 10               | 10          |

| Cc in $\mu F$                     | 2.21                                 | 1.6              | 1.6         |

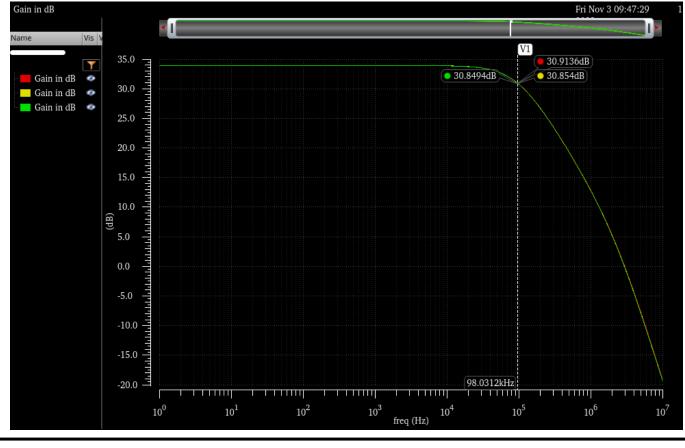

#### **Open Loop Gain, Gain Bandwidth, Phase Margin**

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

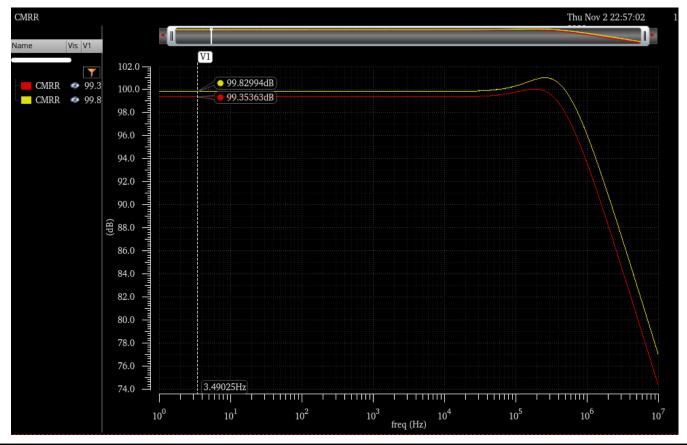

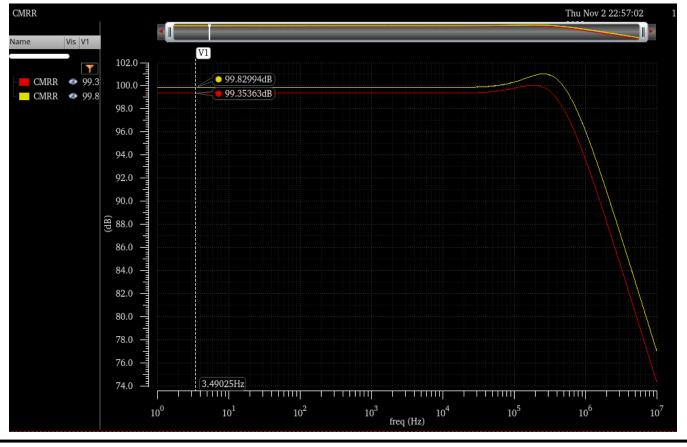

#### **Common Mode Rejection Ratio**

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

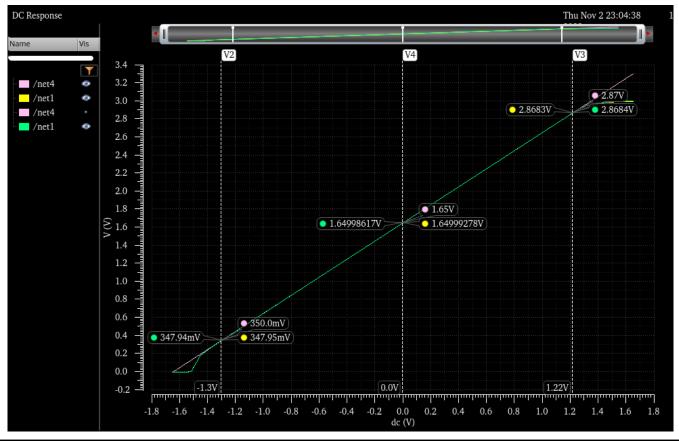

#### Input Common Mode Range, Offset

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

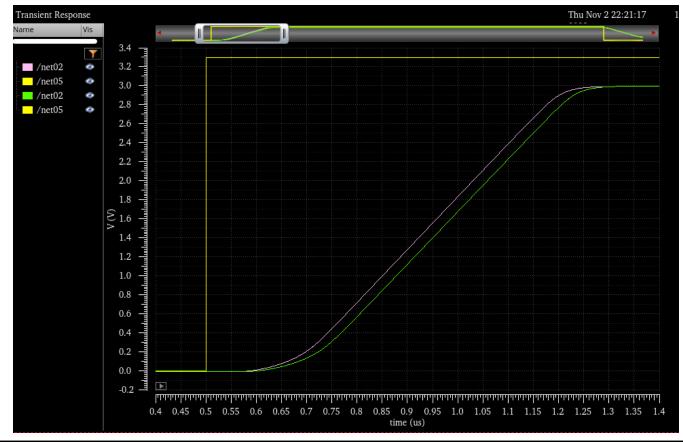

#### **Slew Rate**

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

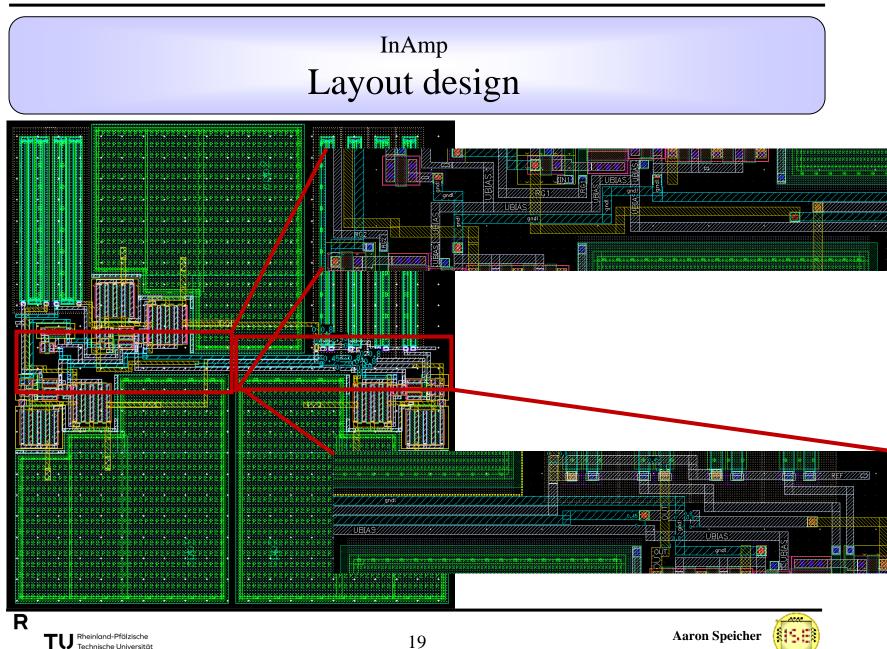

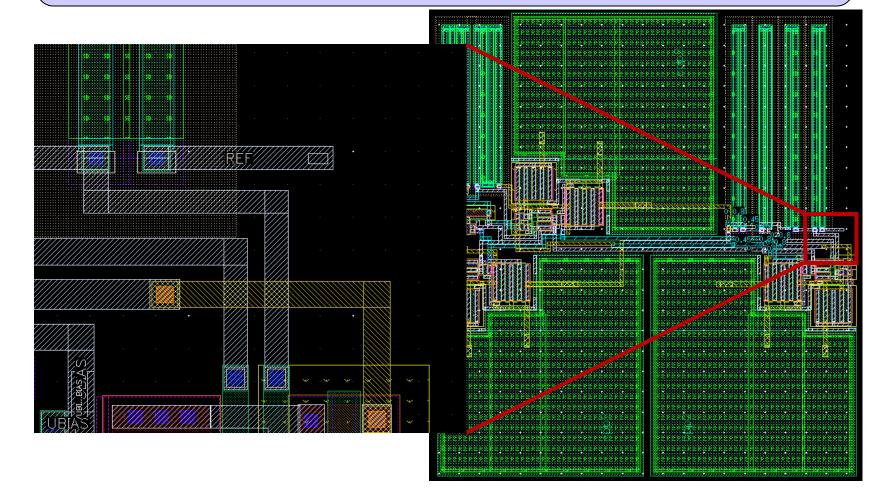

#### InAmp Layout design Find optimal arrangement for short signal paths Minimize area by using • minimum design rules 000000000 000000000000 P3 P3 P3 P3 Run: "InAmp\_LVS" (auf iseserver002) P34P3 Run: "InAmp\_LVS" from /home/tl23\_speicher/AssuraLVS Schematic and Layout Match. You currently have an open run (project). Do you want to close current project and view the results of new run? Summary of LVS Issues 1922 Extraction Information: 0 cells have 0 mal-formed device problems 0 cells have 0 label short problems Quantus Run (auf iseserver002) 0 cells have 0 label open problems Comparison Information: The Quantus run "InAmp\_LVS" completed successfully The output is in : 0 cells have 0 Net mismatches P2 P2 P2 P2 P2 292929292929 0 cells have 0 Device mismatches Library: TESYS\_PROJECT\_AS 0 cells have 0 Pin mismatches 0 cells have 0 Parameter mismatches Cell: InAmp View: analog\_extracted an in the second se ELW Information: 4 Close Total DRC violations: 0 2**7**27272727272727272727 Yes No ) Help R

TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

Kaiserslautern

Landau

Ρ

#### InAmp Layout design

#### InAmp Layout design

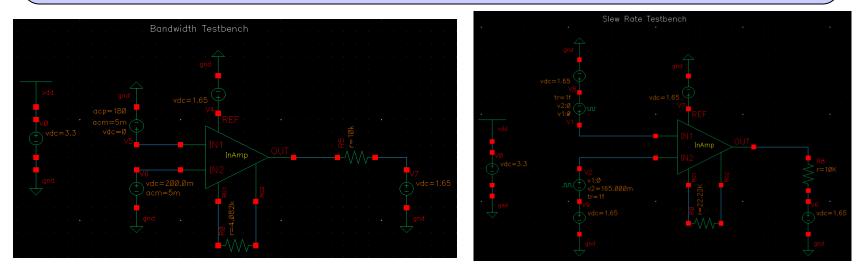

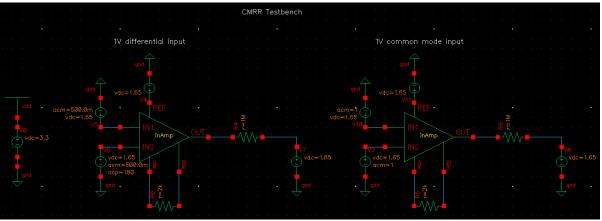

#### InAmp Simulation schematics

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

#### InAmp

#### Post layout simulation and comparison to commercial InAmp

|                                   | Design Result | Post Layout<br>(ideal<br>connections) | Post Layout | INA350 |

|-----------------------------------|---------------|---------------------------------------|-------------|--------|

|                                   |               |                                       |             |        |

| Output Resistance                 | 7.88          | 8.12                                  | 6.78        | -      |

| Slew Rate in V/µs                 | 1.97          | 1.93                                  | 1.92        | 0.24   |

| Common Mode Rejection Ratio in dB | 122           | 121.8                                 | 126.5       | 95     |

| Bandwidth in kHz, G=10            | 473           | 467                                   | 467         | 100    |

| Bandwidth in kHz, G=50            | 98.03         | 96.67                                 | 96.57       | 25     |

| Gain Error in % G=10              | 0.095         | 0.095                                 | 0.105       | 0.05   |

| Gain Error in % G=50              | 0.19          | 0.2                                   | 0.22        | 0.082  |

#### InAmp Post layout simulation

#### Bandwidth G=50

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

#### InAmp Post layout simulation

#### **Common Mode Rejection Ratio**

R TU Rheinland-Pfälzische Technische Universität Kaiserslautern Landau

### Conclusion

- Miller type OpAmp reaches minimum specification, especially Phase Margin (after layout and extract)

- Successful design of current biasing circuit

- Final InAmp design outperforms commercially available INA350 (after layout and extract)

- Square footprint of final InAmp layout

- Possible improvements:

- Matched resistors in InAmp layout

## Thank You for your attention!

### References

- Lecture and lab material of Elektronik II subject by Prof. Koenig

- Lecture and lab material of TESYS subject by Prof. Koenig