Institute of

Cognitive Integrated Sensor Systems

Prof. Dr.-Ing. Andreas König

Dynamically Reconfigurable Mixed-Signal Electronics for Embedded and Intelligent Sensor Systems

Subject:

Investigation of circuit reconfiguration concepts in CMOS technology to improve

analog and mixed-signal components of measurement, instrumentation and sensor

systems with regard to flexibility, accuracy, reliability, stability, and

fault-tolerance. In particular, dynamic reconfiguration concepts, related

to the self-x features of the emerging field of Organic Computing are developed.

The research is both hardware and software oriented and finally aims on the

improvement of established embedded systems architecture. This page reports on the hardware design activities.

Abstract:

The

vivid field of sensor technology delivers an ever increasing number of different

sensor principles and their combination in integrated smart sensor systems for

application in automation, measurement and instrumentation. The corresponding

sensor modules based on single or multi sensor information processing, though

often featuring considerable digital processing capability and digital

interfacing and communication, still heavily depend on the availability of

accurate and reliable analog signal conversion and primary processing. Such

electronics are notorious for the vulnerability with

regard to manufacturing and environmental influences. The notion of a fault is much less

easier to define than for purely digital systems and more sophisticated methods

for detection and compensation of erroneous or unsatisfying system performance

must be devised. Traditional approaches base on calibration

or trimming approaches from design to manufacturing time. Only a few

restricted approaches, such as auto-zeroing techniques or the employment of an

additional DAC for voltage offset compensation, offer dynamic correction

during actual operation time, and, thus, can cope with time varying influences.

An additional problem is the fact, that analog electronics in the majority of

the cases is still designed hard-wired, contrasting the flexibility of the

digital counterpart embodied by FPGA circuits. The research work in this project

draws on the work done in the fields of Neural Network

Hardware, Evolvable Hardware, Reconfigurable

Computing Systems and Organic Computing and

puts it together into a perspective that offers solutions to the challenges raised

above. Comparable to to digital field-programmable sytems, analog counterparts

become available on different levels of granularity (Field-Programmable

Transistor-Arrays (FPTA), Field-Programmable-Analog-Arrays (FPAA),

-Mixed-Signal-Arrays (FPMA)), that allow the flexible configuration of

conventional analog signal processing systems or the learning creation of

application-specific circuits as well as their continuous correction or

reconfiguration by techniques from Evolutionary

Computation. The availability of an innovative field-programmable structure with

scalable passive and active components combined with appropriate algorithms

running on the digital system partition will provide the leverage for dynamic

system reconfigurarion and self-x features. e.g., self-calibration,

self-trimming, self-testing, self-repairing or -healing, for general

embedded systems. A sketch of a general aspired

architecture of an innovative embedded system for sensor applications in automation and instrumentation is given in the

following.

The concept, of course is not limited to the analog front-end, but could also be extended to the backend, dealing with analog and mixed-signal electronics for actuator control. However, for convenience reasons, the current work focuses without restriction of generality just on aspects of sensor signal processing/conditioning electronics and related sensor fusion aspects.

Though remarkable success with regard to the raised challenges and approach can be and has be achieved by academic and industrial institutions, the focus on this work is, however, on observed deficiencies and open issues for practical and successful industrial application. For instance, state-of-the-art hardware FPAA/TA structures and the circuits resulting from evolutionary optimisation may not comply with the established circuits and proven standards in the automation and instrumentation community. Thus, the behaviour of freely evolved circuits can be black-box and somewhat unpredictable. This strongly contradicts ever increasing quality and reliability demands in todays industry. Also, practical requirements on adaptation algorithms with regard to convergence time, solution quality and resource availability make further innovations mandatory. Correspondingly adapted hardware/software structures in an unifying approach are subject of our current research and development.

In the first investigations, operational amplifiers (OPA) as essential building blocks for analog and mixed-signal electronics were investigated with regard to suiting reconfigurable implementation. In contrast to most existing field-programmable chips, an approach of medium granularity was chosen to both incorporate existing design knowledge by imposing structure as well as minimizing the number of required switches. The minimization of switches will reduce the chip complexity, lower reconfiguration time, i.e. allows for faster reconfiguration cycles and, last not least, will reduce the number of parasitic capacitances and resistances of the design. Further, similar to scaling networks in ADC/DAC, scaling elements for OPA design were constituted from basic elements scaled by powers of two. For instance, the Miller-OPV studied as one of the first amplifier instances consists of scalable PMOS and NMOS transistor blocks of 11 configuration bits along with a corresponding scalable compensation capacitor. The design was carried out empoying Austriamicorsystems 0.35 microns CMOS technology. Based on fixed channel length and appropriate aspect ratio settings, the behavior of a standard Miller-OPA with the schematic version of the reconfigurable one, as well as with the extracted netlist of a hard-wired tentative layout version in the chosen technology was carried out.

The achieved results encouraged our research work, as the applicability of the concept for practical applications could be confirmed by the simulations. The reconfigurable nature of the design carries the promise, that the minor deviations observed in the ac-analysis of the physical circuit could be compensated by approriate reconfiguration. The design currently is completed by digital shift register cells for the sake of a simple control interface and package. For future, increasingly complex designs in the aspired family, random access digital memory and further established concepts, such as shadow memory, will also be considered for implementation. Other amplifier topology, such as folded-cascode versions, were also subject of study and implementation with comparable results, which can be extracted from achieved publications.

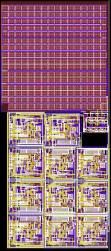

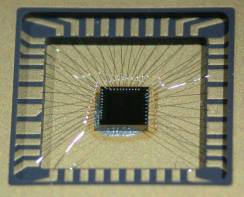

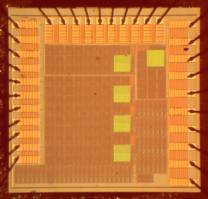

Further, on the next level of abstraction, circuits of multiple amplifiers and feedback networks for sensor signal conditioning/preprocessing have investigated. An instrumentation amplifier has been implemented as the first case study. The folowing pictures show the first implemented chip FPMA-1 with three different amplifier types:

The simulations results were confirmed for the Miller and Folded-Cascode cells by a simple prototype, that allows programming of the reconfigurable amplifier blocks.

A t entative list of specification values is given for the first investigated configurations:

The system is also employed in teaching from summer 2007. Students of a integrated mixed-signal design course size and implement amplifiers according to requested specifications in the same CMOS technology. In addition to post-layout simulations, they generate a configuration pattern and measure there sizing based on the FPMA-1.

The recent configurations, comprising the basis for the hardware design, have still been determined following traditional design plans and practice. In the second, software-related part of the work, inspirations from analog circuit and system synthesis as well as evolutionary electronics are picked up and employed to develop appropriate dynamic reconfiguration algorithms and corresponding simulation enviroment for the previously described novel hardware structures. The principle concept,which bears a strong inspiration by the Chip-In-the-Loop-Learning introduced by Intel for their ETANN-Chip, is coarsely illustrated in the following:

The main difference is, that proprietary genetic algorithms or evolutionary algorithms are employed together with appropriate multi-objective optimization and fitness functions. Key aspects are the inclusion of a priori knowledge as well as principles from self-organization into the optimization scheme to achieve rapid convergence and reliable, predictable system behavior. For the reported work, the bit patterns to configure or reconfigure the dynamically reconfigurable amplifier are generated off-line by the simulation environment. Now an enhanced simulation environment has been developed and and partially deployed to the respective embedded system to configure and update the mixed-signal electronics concurrently to its operation, i.e. on-line, in an application environment. The work on the prototype of such an enhanced embedded system, that hosts the dynamically reconfigurable OPA and runs an embedded version of the reconfiguration algorithm outlined above is reported on a separate page.

OPA topology determination by a switching pattern and a more complex array chip are currently under investigation. Sufficient ST and switching resources for the most common basic amplifier topologies will be provided and scalable passive components for the feedback networks will be added. The aspired long term result of our research will be an FPAA-like flexibly and dynamically configurable circuit with self-trimming, -testing, and repairing properties for adaptive sensor electronics. We aspire the results of this work to be a salient contribution and innovation to both industrial systems in measurement, instrumentation, and automation as well as in research fields, such as Reconfigurable Computing Systems and Organic Computing. The latter fields are currently dominated by digital approaches, inspite of the fact that analog and mixed-signal components represent as small yet decisive system partition crucial for the overall performance. Further, potential limitations will considered, which are expected with regard to feasible bandwidth and low-power design issues. In the latter case of low-power design, our work can benefit from the results achieved in a previous project funded by DFG (SPP VIVA, GAME/GAMPAI), where the low-power design of trainable or partly reconfigurable classifier circuits in subthreshold was carried out.

| Status: | concluded, duration 01/2004-05/2007 | ||

| Partner: | PHYTEC Messtechnik GmbH, Robert-Koch-Strasse 39, 55129 Mainz | ||

| Financing: | PHYTEC Messtechnik GmbH, Robert-Koch-Strasse 39, 55129 Mainz | ||

| Contact: | Prof. Dr.-Ing. Andreas König | ||

| Contributors: | Senthil Kumar Lakshmanan and Andreas König | ||

| Publications: | |||

| Lakhsmanan, S. K.; König, Andreas: "A Contribution to Reconfigurable Analog Electronics by a Digitally Programmable Sensor Signal Amplifier" Kleinheubacher Tagung, Workshop Integrierte digitale und analoge Schaltungen, Miltenberg, Germany, 27. Sept. - 01. Oct., 2004. | |||

| Lakhsmanan, S. K.; König, Andreas: "Reconfigurable Amplifier Circuits for Adaptive Sensor Systems Employing Bio-Inspiration" in Proc. of the 4th Int. Conf. on Hybrid Intelligent Systems HIS´04, IEEE CS, pp. 38-43, Kitakyushu, Japan, 5-8 Dec., 2004. | |||

| König, Andreas: "Status of Adaptive Sensor Electronics and its Perspective as a Base Technology for Ambient Intelligence and Organic Computing" Plenary in Proc. of the NCEI´04, pp. 17-18 , KEDRI, Auckland, New Zealand, 2004 | |||

| König, Andreas. Dynamically Reconfigurable Electronics for Smart Sensor Systems. Invited Talk at the International Conference on Instrumentation, Communications and Information Technology ICICI 05, Institute Teknologi Bandung, Bandung, Indonesia, August 3-5, 2005. |