Institute of

Cognitive Integrated Sensor Systems

Prof. Dr.-Ing. Andreas König

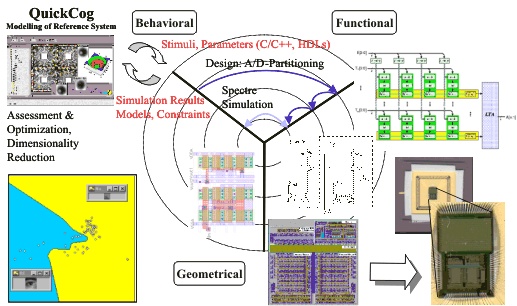

GAME - Holistic Modelling of Recognition Systems

Subject:

Investigation of novel design concepts for low-power CMOS sensing and recognition system implementation. Combination of holistic modelling and reconfiguration and adaptation concepts for the integration

of lean, low-power analog or mixed-signal intelligent systems with inherent fault-tolerance and yield increase.

Abstract:

In this project, based on the wealth of existing low-power analog and mixed-signal signal processing and neural circuits, a design methodology was elaborated for intelligent integrated systems, that employs holistic modelling and reconfiguration & adaptation concepts to achieve well-performing, low-power, and dependable embedded/integrated system implementation. A particular focus was on the implementation of recognition tasks in intelligent systems, e.g., facial feature classification for face detection and tracking (eye-tracking to control a 3D-display) or similar tasks of car detection and tracking from the automative field of driver assistance systems, e.g., overtake

monitoring. In-line inspection, biometric systems, or additional driver assistance tasks, such as drowsiness detection, show similar properties.

For this aim, based on a austriamicrosystems 0.6 microns CMOS technology, a cell library of low-power circuits for classifiers, e.g., BP, CasCor, RCE, RBF, PNN, kNN, RNN, or LVQ as well as feature extraction methods, e.g., convolution, correlation, gabor filters etc. was developed under cascadability and reconfigurability constraints. For the behavioral modelling of the aspired recognition systems, the QuickCog system developed in concurrent research work in the group, was employed. In addition to the human-centered design activities, QuickCog supports also features of automated design by inherent visual and numerical quality measures and optimization mechanisms, that minimize required computational & implementation effort, and, thus, power consumption, while assuring the performance of the recognition system.

For consistent design and circuit/sizing assessment, in the first step of the work, interfaces were created, that translated signal or feature data as well as classifier contents to electrical stimuli in the Cadence DFW II. The result of circuit simulation was fed back to the QuickCog platform for assessment and comparison with the reference system results.Thus, low-power circuit aptness for the regarded problem could systematically be assessed for nominal as well as statistical design analysis.

In the next step of the work, inspired by the concept of chip-in-the-loop-learning, introduced by Intel for optimizing their ETANN´s chip performance, inclusion of circuit imperfections in the learning loop for advanced compensation was considered.

Such a compensation can be employed after chip manufacturing, as in the case of Intel´s ETANN, which requires modifiable or reconfigurable redundant resources in the chip circuits. Also, at design time the concept can employed by incorporating circuit in the training loop. The modifiable or reconfigurable resources in this case are. e.g., sizing parameters or topological variations of the circuit. In the research activity, behavioral models on various levels of abstraction have been employed and simulations for the determination of application-specific sizing and required reconfiguration ressources determination for low-power yet reliably at high yield performing mixed-signal circuits have been started. Also, the sole use of gradient decent techniques in the learning loops has been enhanced by use of evolutionary computing techniques. In the concurently developing field of Evolvable Hardware, the notions of intrinsic and extrinsic evolution have been coined for the above mentioned optimization approaches.

In the project, three chip for low-power vision and classification have been designed and manufactured. More information can be obtained from a Game-project book chapter (publication pending) of a book dedicated to the priority programme.

The research work has given the baseline for the currently pursued work on low-power, dependable sensor electronics and systems with self-x capabilities. In particular, the focus of the recent work is on the demands of wireless autonomous or self-sufficient sensory systems, e.g., required for ambient intelligence, ubiquitous computing, and industrial automation. Further, vulnerable amplitude coding still pursued in GAME is left behind in more recent work in favor of timely spike coded signal processing and circuits for future dependable embedded systems.

| Status: | concluded, duration 08/1999-09/2002 | ||

| Partner: | - | ||

| Financing: | Deutsche Forschungsgemeinschaft DFG, SPP 1076 VIVA | ||

| Contact: | Prof. Dr.-Ing. Andreas König | ||

| Contributors: | Jens Döge, Michael Eberhardt (Research Assistants) Robert Wenzel, Andre Kröhnert, Andre Günther, Tilo Grohmann (student contributors) | ||

| Publications: | |||

| König, A., Skribanowitz, J., Schreiter, J., Getzlaff, S., Eberhardt, M., Wenzel, R. Ein System zur schnellen Modellierung von Bildverarbeitungs- und Erkennungssystemen. In Tagungsband der Dresdner Arbeitstagung Schaltungs- und Systementwurf DASS'98, FhG IIS-EAS, Dresden, 26. Mai, 1998. | |||

| König, A., Eberhardt, M., Döge, J., Skribanowitz, J., Gü:nther, A., Wenzel, R.: Quantitative Measures for Systematic Optimization and Validation in the Parsimonious Dersign of Application-Specific Vision and Cognition Systems. In Proc. of the 3rd Workshop on System Design Automation - SDA 2000, March 14-15, Rathen, Germany, pp. 122-129, 2000. | |||

| König, A., Grohmann, T., Günther, A., Kröhnert, A., Eberhardt, M., Wenzel, R., Döge, J.: Erweiterung der Entwurfshierarchie zur schnellen und konsistenten VLSI-Modellierung von anwendungsspezifischen verlustarmen Bildverarbeitungs- und Erkennungssystemen. In Dresdner Arbeitstagung Schaltkreis- und Systementwurf DASS'2000, Dresden, May, 2000. | |||

| A.

König, M. Eberhardt, J. Döge, J. Skribanowitz, A. Günther, R. Wenzel, and T.

Grohmann. Quantitative Measures for Systematic Optimization, Validation, and

Imperfection Compensation in the Holistic Modeling and Parsimonious Design of

Application-Specific Vision and Cognition Systems. In System Design Automation - Fundamentals, Principles, Methods, Examples, R. Merker and W. Schwarz (Eds.), Kluwer, pp. 247-258, 2001. |

|||

| C. Mayr and A. König. Low-Power Massively Parallel Feature Computation for Application-Specific Integrated Vision Systems. 6th on-line world conference on soft computing WSC6, September, 2001. | |||

| A. König, M. Eberhardt, J. Döge, R. Wenzel, J. Skribanowitz. Perspektive des Entwurfs verlustleistungsarmer integrierter Signalverarbeitung für intelligente Mikrosensoren in lernender Architektur. Eingeladener Vortrag, In Tagungsband GMA-Kongress 2001 Automatisierungstechnik im Spannungsfeld neuer Technologien, 22./23. Mai, Kongresshaus Baden-Baden, S. 61- 68, 2001. | |||

| A. König, C. Mayr, T. Bormann, and C. Klug. Dedicated Implementation of Embedded Vision Systems Employing Low-Power Massively Parallel Feature Computation. In Proc. of the 3rd VIVA-Workshop on Low-Power Information Processing, pages 1-8, Chemnitz, Germany, March, 18-19, 2002. |